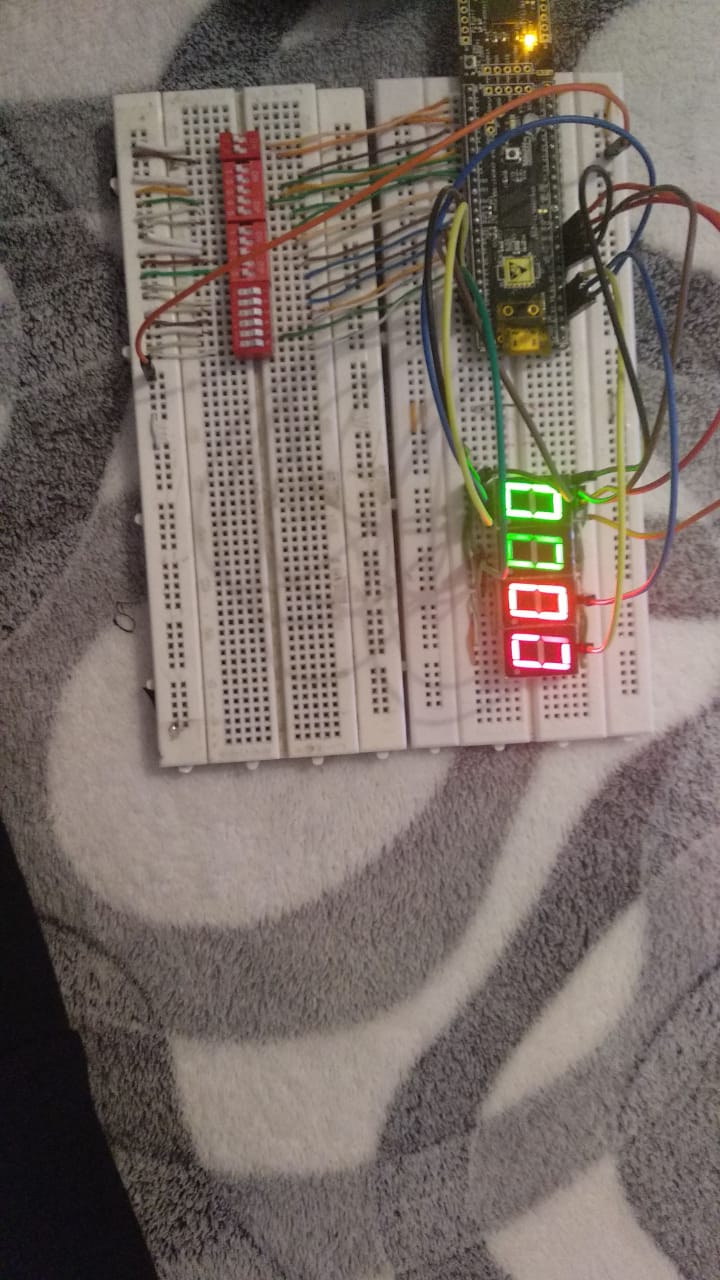

En este laboratorio se realizo un sumador- restador de 8 bits y el resultado fue mostrado en 3 displays de 7 segmentos.

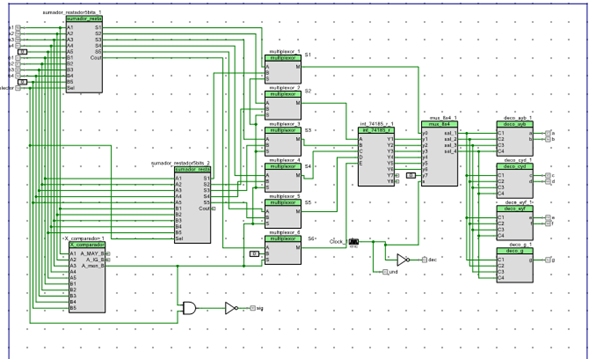

Este proyecto tendrá 17 entradas las cuales se dividirán de la siguiente forma, 8 bits del primer dígito, 8 bits del segundo dígito y un bit para saber si debe sumar o restar.

El primer componente que creamos fue un conversor de binario a BCD, esto lo hicimos con el integrado 74185 y la conexión fue la siguiente:

Sabemos que el integrado 74185 es un componente que ya esta creado, de todas maneras pongo su tabla de verdad a continuación:

Para poder hacer la visualización dinámica se deben tener la misma salida para los leds de los 7 segmentos. Solo una va a ser diferente en cada una que en este caso va a ser el pin de la tierra (común). Para ello debemos separar los bits de mas a menos significativo, y hacer alumbrar los displays de manera separada, pero con frecuencias lo suficientemente altas para que el ojo humano logre ver como si los 3 estuvieran prendidos.

Luego se realizara un mux 16:4 con el fin de que agrupe los datos sumados y restados en el anterior paso. Para crear este se hace con mux 2:1 (creados originariamente en Psoc Creator) y luego se van haciendo conexiones entre ellos para así llegar al Mux de 16:4.

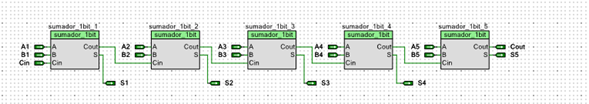

Para crear el sumador de 5 BITS hay una entrada disponible en el blog donde se explica mas a detalle.

Para el restador, lo que se hizo fue sacar el complemento A2 del numero deseado. Como ya sabemos si sumamos un numero con otro que posee complemento A2 estaremos realizando la operación resta.

Por ultimo se utilizo el decodificador de BCD a 7 Segmentos (creado a detalle en otra entrada del blog). Asi quedo finalmente nuestro proyecto.

Asi fue implementado en la PSOC: